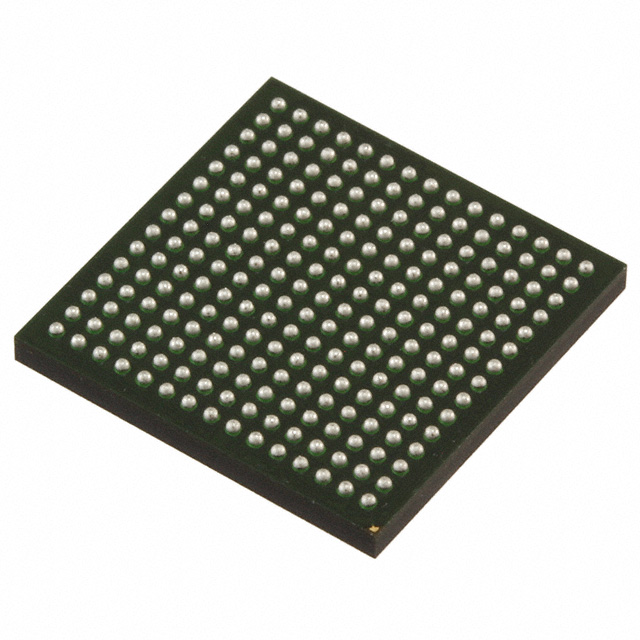

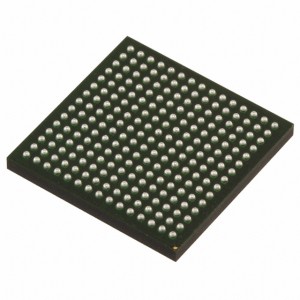

XC7Z007S-1CLG225I IC SOC CORTEX-A9 667MHZ 225BGA componentes eletrônicos chips ic circuitos integrados próprio estoque BOM Serviço

Atributos do produto

| TIPO | DESCRIÇÃO |

| Categoria | Circuitos Integrados (ICs) |

| Fabricante | AMD Xilinx |

| Series | Zynq®-7000 |

| Pacote | Bandeja |

| Pacote padrão | 160 |

| Status do produto | Ativo |

| Arquitetura | MCU,FPGA |

| Processador principal | Único ARM® Cortex®-A9 MPCore™ com CoreSight™ |

| Tamanho do Flash | - |

| Tamanho da RAM | 256 KB |

| Periféricos | DMA |

| Conectividade | CANbus, EBI/EMI, Ethernet, I²C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Velocidade | 667 MHz |

| Atributos Primários | Artix™-7 FPGA, células lógicas de 23K |

| Temperatura de operação | -40°C ~ 100°C (TJ) |

| Pacote/Caso | 225-LFBGA, CSPBGA |

| Pacote de dispositivos do fornecedor | 225-CSPBGA (13×13) |

| Número de E/S | 54 |

| Número básico do produto | XC7Z007 |

China aprova aquisição da Xilinx pela AMD com 5 condições!

Em 27 de outubro de 2020, a AMD anunciou que irá adquirir a Xilinx (Xilinx) por US$ 35 bilhões em um acordo com todas as ações.O acordo, embora aprovado por unanimidade pelos conselhos de administração de ambas as partes, ainda precisa de ser aprovado pelos acionistas de ambas as partes, com aprovação regulamentar de vários países, incluindo, claro, a China.

Recentemente, o Gabinete Antimonopólio da Administração Estatal de Supervisão e Administração de Mercado da China anunciou a decisão de aprovar a revisão antimonopólio da aquisição de uma participação na Xilinx pela Chaowei Semiconductor Corporation com condições restritivas adicionais (o “Anúncio”), aprovando a aquisição da Xilinx pela AMD e a eliminação do obstáculo regulatório final para a aquisição.

De acordo com o Anúncio, após um ano de recebimento da declaração antimonopólio de concentração de operadora no caso da aquisição da Xilinx pela AMD em 19 de janeiro de 2021, e do arquivamento do caso após o requerente complementar seus materiais de declaração, a Administração Geral de Regulação de Mercado (GAMR) decidiu aprovar o caso com condições restritivas.

As fusões são permitidas, mas não há vendas agrupadas ou discriminação contra clientes chineses

É importante compreender que as aquisições com operações transfronteiriças requerem aprovação regulamentar de vários reguladores importantes do mercado em todo o mundo.Anteriormente, os EUA, o Reino Unido e a UE já tinham autorizado a aquisição, e agora que a China aprovou o caso, significa que a AMD poderá concluir os seus planos de aquisição no primeiro trimestre de 2022.

Deve-se notar, no entanto, que a aprovação da aquisição da Xilinx pela AMD pela Administração Geral Chinesa de Regulação de Mercado vem com condições restritivas adicionais, exigindo que ambas as partes na transação e a entidade pós-concentração cumpram as seguintes obrigações.

(i) Ao vender CPUs SuperPower, GPUs SuperPower e FPGAs Celeris para o mercado na China, eles não deverão de forma alguma obrigar vendas vinculadas ou anexar quaisquer outras condições comerciais não razoáveis;não impedirão ou restringirão os clientes de comprar ou utilizar os produtos acima mencionados individualmente;e não discriminarão os clientes que compram os produtos acima individualmente em termos de nível de serviço, preço, recursos de software, etc.

(b) Promover ainda mais a cooperação relevante com base na cooperação existente com empresas na China e continuar a fornecer CPUs Chaowei, GPUs Chaowei, FPGAs Xilinx e software e acessórios relacionados ao mercado na China seguindo os princípios de justiça, razoabilidade e não- discriminação.

(iii) Garantir a flexibilidade e programabilidade dos FPGAs da Xilinx, continuar a desenvolver e garantir a disponibilidade da linha de produtos FPGA da Xilinx e garantir que ela seja desenvolvida de maneira compatível com processadores baseados em ARM e de acordo com os planos da Xilinx antes da Transação .

(iv) continuar a garantir a interoperabilidade das CPUs Chaowei, GPUs Chaowei e FPGAs Celeris vendidos no mercado da China com CPUs, GPUs e FPGAs de terceiros;o nível de interoperabilidade acima referido não deve ser inferior ao nível de interoperabilidade das CPU Chaowei, GPU Chaowei e FPGA Celeris;informações, recursos e amostras relacionadas à atualização de interoperabilidade deverão ser fornecidas a terceiros dentro de 90 dias após a atualização dos fabricantes de CPU, GPU e FPGA.

(v) Tomar medidas para proteger as informações dos fabricantes terceirizados de CPU, GPU e FPGA e celebrar acordos de confidencialidade com os fabricantes terceirizados de CPU, GPU e FPGA;armazenar as informações confidenciais de fabricantes terceirizados de CPU, GPU e FPGA em sistemas de hardware separados e mutuamente exclusivos.

.png)